隨著物聯(lián)網(wǎng)、可穿戴設(shè)備及生物醫(yī)療電子等領(lǐng)域的飛速發(fā)展,對(duì)電子器件提出了更高要求:在保持甚至提升性能的必須實(shí)現(xiàn)小型化、輕量化、高集成度,并具備出色的柔性與共形能力。基于層疊網(wǎng)格的設(shè)計(jì)范式,為高集成度小型化柔性電子器件的實(shí)現(xiàn)開辟了一條極具潛力的技術(shù)路徑。

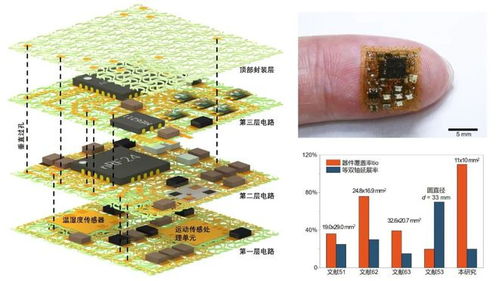

層疊網(wǎng)格設(shè)計(jì)的核心在于將傳統(tǒng)二維平面電路與元器件,通過精密設(shè)計(jì)與制造工藝,在三維空間內(nèi)進(jìn)行垂直堆疊與集成。這種結(jié)構(gòu)充分利用了Z軸方向的空間,從而在有限的平面投影面積內(nèi),大幅提升了功能密度。網(wǎng)格化則是指將互聯(lián)線路、功能單元(如傳感器、晶體管、天線、儲(chǔ)能單元等)以網(wǎng)格狀圖案進(jìn)行布局與連接。這種網(wǎng)格結(jié)構(gòu)不僅提供了機(jī)械柔性所需的可拉伸、可彎曲特性,還確保了電信號(hào)與能量在復(fù)雜形變下的穩(wěn)定傳輸與分布。

在高集成度小型化柔性電子器件的具體設(shè)計(jì)中,層疊網(wǎng)格技術(shù)展現(xiàn)出多方面的優(yōu)勢(shì):

- 空間利用率最大化:通過多層薄膜材料的堆疊,將傳感、處理、通信、供能等不同功能的模塊垂直集成于同一器件內(nèi),實(shí)現(xiàn)了系統(tǒng)級(jí)芯片(SoC)或系統(tǒng)級(jí)封裝(SiP)在柔性基底上的類比,顯著縮小了器件整體 footprint。

- 異質(zhì)集成與功能多樣化:層疊結(jié)構(gòu)允許在不同層級(jí)使用不同的材料(如半導(dǎo)體、導(dǎo)體、介電體、彈性體)和工藝。例如,底層可集成硅基CMOS芯片用于高性能計(jì)算,中間層布置有機(jī)半導(dǎo)體傳感器或石墨烯電極,頂層則構(gòu)建柔性天線或能量收集器,從而實(shí)現(xiàn)硅基高性能與新興柔性材料的優(yōu)勢(shì)互補(bǔ)。

- 性能優(yōu)化與干擾抑制:精心設(shè)計(jì)的層間介電層和網(wǎng)格化地/電源平面,可以有效隔離數(shù)字、模擬、射頻等不同功能電路,減少串?dāng)_和電磁干擾,提升整體信噪比和系統(tǒng)穩(wěn)定性,這對(duì)于高度集成的混合信號(hào)系統(tǒng)至關(guān)重要。

- 機(jī)械魯棒性與柔性增強(qiáng):網(wǎng)格化的互聯(lián)線路本身具有可拉伸性,而層疊結(jié)構(gòu)通過中性機(jī)械面設(shè)計(jì),可以將脆性功能組件(如硅芯片)置于應(yīng)變中性層,使其在器件彎曲、拉伸時(shí)承受最小應(yīng)力,從而保護(hù)核心元件,實(shí)現(xiàn)整體器件的可靠柔性。

實(shí)現(xiàn)基于層疊網(wǎng)格的高性能柔性電子器件也面臨諸多挑戰(zhàn):

- 制造工藝復(fù)雜性:需要開發(fā)與柔性基底兼容的精密多層圖形化、對(duì)準(zhǔn)、薄膜沉積及互連穿孔(via)技術(shù),工藝溫度、應(yīng)力控制要求極高。

- 熱管理難題:高集成度帶來功率密度上升,在柔性、透氣性往往不佳的疊層結(jié)構(gòu)中散熱成為瓶頸,需引入導(dǎo)熱通路或新型冷卻機(jī)制。

- 可靠性與耐久性:在反復(fù)彎折、拉伸等動(dòng)態(tài)機(jī)械載荷下,層間界面結(jié)合強(qiáng)度、互聯(lián)導(dǎo)線的疲勞壽命是決定器件長(zhǎng)期可靠性的關(guān)鍵。

- 設(shè)計(jì)自動(dòng)化工具缺失:與傳統(tǒng)剛性PCB或IC設(shè)計(jì)相比,適用于三維柔性層疊網(wǎng)格結(jié)構(gòu)的EDA工具尚不成熟,設(shè)計(jì)周期長(zhǎng),優(yōu)化困難。

未來發(fā)展趨勢(shì)將集中于新材料(如二維材料、液態(tài)金屬)、新工藝(如轉(zhuǎn)印、增材制造)、以及跨尺度的協(xié)同設(shè)計(jì)方法。通過材料、結(jié)構(gòu)、工藝與電路設(shè)計(jì)的深度融合,基于層疊網(wǎng)格的柔性電子器件有望在智能皮膚、植入式醫(yī)療設(shè)備、柔性顯示和共形天線等領(lǐng)域?qū)崿F(xiàn)革命性應(yīng)用,真正將高度智能的電子系統(tǒng)無縫集成到我們的生活和環(huán)境中。